### Performance Improvement of ISM 5.8 GHz Transceivers

Submitted by

### Anh Ngoc Nguyen

M.Sc. Science B.Sc. Electronics and Telecommunications

A thesis submitted in total fulfilment of the requirements for the degree of

### **Doctor of Philosophy**

Centre for Technology Infusion School of Engineering and Mathematical Sciences College of Science Health and Engineering

La Trobe University

Victoria 3086 Australia

February 2021

Dedicated to my beloved wife and son

Hang Doan & An Ngayen

## **Table of Contents**

| Tab  | ole of Co | onte  | nts                                           | III   |

|------|-----------|-------|-----------------------------------------------|-------|

| List | t of Figu | ires. |                                               | VII   |

| List | t of Tab  | les   |                                               | XV    |

| List | t of Abb  | orevi | iations                                       | XVI   |

| List | t of Sym  | ibols | S                                             | XVIII |

|      |           |       | uthorship                                     |       |

|      |           | 0     | ent                                           |       |

|      |           |       |                                               |       |

|      |           |       | tions                                         |       |

| 1    | 1.1       |       | l <b>uction</b><br>troduction                 |       |

|      |           |       |                                               |       |

|      | 1.2       | M     | otivations                                    | 5     |

|      | 1.2       | 2.1   | High Linearity Power Amplifier Motivations    | 6     |

|      | 1.2       | 2.2   | Harmonic Suppression Antenna Motivations      | 7     |

|      | 1.2       | 2.3   | Full-Duplex Antenna Motivations               | 9     |

|      | 1.3       | Re    | esearch Aims                                  | 11    |

|      | 1.4       | Or    | riginal Contribution of the Thesis            | 13    |

|      | 1.5       | Si    | gnificance of the Research                    | 15    |

|      | 1.6       | Re    | esearch Methodologies and Techniques          | 17    |

|      | 1.7       | Tł    | nesis Organisation                            | 19    |

| 2    | Li        | tera  | ture Review                                   | 21    |

|      | 2.1       | In    | troduction                                    | 21    |

|      | 2.2       | Cl    | MOS Power Amplifier with Linearity Techniques | 21    |

|      | 2.2       | 2.1   | Basic Parameters                              | 23    |

|      | 2.2       | 2.2   | Adaptive Bias                                 | 25    |

|      | 2.2       | 2.3   | Second Harmonic Short Circuit                 |       |

| 2.2.4    | Summary                                              | 34 |

|----------|------------------------------------------------------|----|

| 2.3 Hai  | rmonic Suppression Antenna                           | 35 |

| 2.3.1    | Basic Parameters                                     |    |

| 2.3.2    | Defected Ground Structure                            |    |

| 2.3.3    | Stepped Slot                                         | 42 |

| 2.3.4    | Thin Microstrip Line and MIM Cap                     | 43 |

| 2.3.5    | Summary                                              | 46 |

| 2.4 Ful  | l-Duplex Antenna                                     | 47 |

| 2.4.1    | Basic Parameters                                     | 49 |

| 2.4.2    | Coupler                                              | 49 |

| 2.4.3    | Coplanar Waveguide Configuration (CPW)               | 52 |

| 2.4.4    | Reflective Termination                               | 56 |

| 2.4.5    | Summary                                              | 58 |

| 2.5 Mit  | tigating Activities                                  | 59 |

|          | inearity CMOS Power Amplifier                        |    |

| 3.1 Intr | oduction                                             | 61 |

| 3.2 Pov  | ver Amplifier Design                                 | 63 |

| 3.2.1    | Design Methodology for RF Power Amplifiers           | 63 |

| 3.2.2    | Specifications for 5.8 GHz Power Amplifier Design    | 64 |

| 3.2.3    | Power Amplifier Topology                             | 64 |

| 3.2.3.   | 1 Two-Stage Design                                   | 66 |

| 3.2.3.   | 2 Differential Topology                              | 68 |

| 3.2.3.   | 3 Cascode Amplifier Stage                            | 70 |

| RC       | E Feedback Design                                    | 72 |

| 3.2.4    | Power Amplifier Schematic                            | 73 |

| 3.2.4.   | 1 Second Harmonic Short Circuit                      | 76 |

| 3.2.4.   | 2 On-Chip Transmission Line Transformer (TLT) Design | 77 |

|          |                                                      |    |

3

| HFSS Simulation of the Three TLTs                        | 80  |

|----------------------------------------------------------|-----|

| Current Calculation of TLTs                              |     |

| 3.2.4.3 Linearization with PMOS Adaptive Bias Circuit    |     |

| 3.2.4.4 Small Signal and Large Signal Stability          | 92  |

| 3.2.5 PA Layout Design                                   | 94  |

| 3.2.5.1 Layout                                           | 94  |

| 3.2.5.2 Bondwire Equivalent Models                       | 97  |

| 3.3 Implementation and Experiment Results                | 101 |

| 3.3.1 Printed Circuit Board (PCB) Design                 | 101 |

| 3.3.2 Power and S-parameter Measurement Test Setup       | 102 |

| 3.3.3 Measurement Results                                | 102 |

| 3.4 Summary                                              | 105 |

| Harmonic Suppression Antennas                            | 107 |

| 4.1 Introduction                                         | 108 |

| 4.2 Design Methodology for Harmonic Suppression Antennas | 110 |

| 4.3 Double Slot Harmonic Suppression Antenna             | 112 |

| 4.3.1 Conventional Rectangular Slot Antenna Design       | 113 |

| 4.3.2 Harmonic Suppression Antenna Design                | 114 |

| 4.3.2.1 Defected Ground Slot (DGS)                       | 115 |

| 4.3.2.2 Stepped Impedance Resonator (SIR)                | 118 |

| 4.3.2.3 Bandwidth of SIR                                 | 120 |

| 4.3.2.4 MIM Cap                                          | 124 |

| 4.3.3 Simulation and Measurement Results                 | 125 |

| 4.3.4 Summary                                            | 127 |

| 4.4 A Small-Size Slot Harmonic Suppression Antenna       | 127 |

| 4.4.1 Harmonic Suppression Analysis                      | 128 |

| 4.4.2 Simulation and Measurement Results                 | 131 |

| 4.4.3 Summary                                            | 134 |

|      | 4.5 W  | videband Triangle Slot Antenna with Out-of-Band Rejection | 134         |

|------|--------|-----------------------------------------------------------|-------------|

|      | 4.5.1  | Simple Triangle Slot Antenna                              | 136         |

|      | 4.5.2  | Wideband and Compact Slot Antenna with Harmonic Supp      | pression138 |

|      | 4.5.3  | Results and Discussions                                   | 141         |

|      | 4.5.4  | Comparison with Other Designs                             | 143         |

|      | 4.5.5  | Summary                                                   | 144         |

|      | 4.6 S  | ummary                                                    | 144         |

| 5    | Full-I | Duplex Antenna                                            | 147         |

|      | 5.1 Ir | ntroduction                                               |             |

|      | 5.2 A  | ntenna Design                                             | 149         |

|      | 5.2.1  | Analysis of Even and Odd Mode in CPW                      | 149         |

|      | 5.2.2  | Isolation Investigation                                   | 151         |

|      | 5.2.3  | Antenna Impedance Investigation                           | 153         |

|      | 5.2.4  | Parameter Study                                           | 156         |

|      | 5.2.5  | Measurement Results                                       | 159         |

|      | 5.3 S  | ummary                                                    | 162         |

| 6    | Concl  | usion                                                     | 163         |

|      | 6.1 C  | ontribution, Major Findings, and Conclusion               | 163         |

|      | 6.1.1  | High Linearity CMOS Power Amplifier                       | 163         |

|      | 6.1.2  | Harmonic Suppression Antenna                              | 164         |

|      | 6.1.3  | Full-Duplex Antenna                                       | 167         |

|      | 6.1.4  | Summary                                                   | 167         |

|      | 6.2 F  | uture Work                                                | 168         |

|      | 6.2.1  | High Linearity CMOS PA                                    | 168         |

|      | 6.2.2  | Harmonic Suppression Antenna                              | 169         |

|      | 6.2.3  | Full-duplex Antenna                                       | 169         |

| Refe | rences |                                                           | 171         |

# **List of Figures**

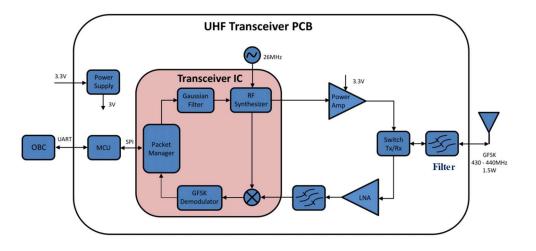

| Figure 1-1. Block diagram of a typical RF Transceiver Module [1]. The PA and the low noise amplifier (LNA) are connected to the antenna through a switch and a filter                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

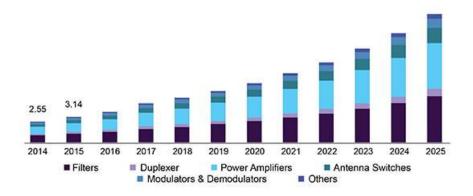

| Figure 1-2. RF component market size [3]. The PA segment occupies a large portion, more than 30%, of the overall RF market share                                                                                                                                            |

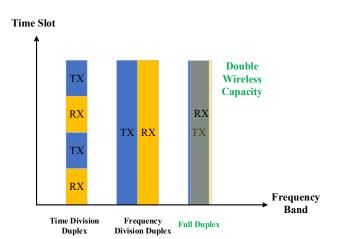

| Figure 1-3. Full-duplex operation doubles wireless capacity [28]                                                                                                                                                                                                            |

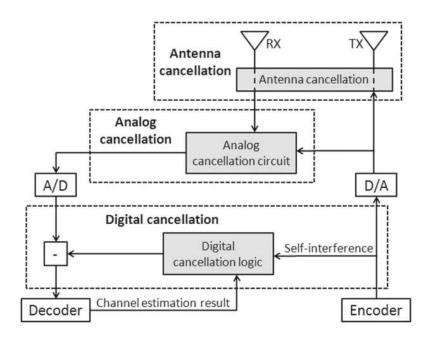

| Figure 1-4. Block diagram of a typical full-duplex system [31]. The SI cancellation techniques should be implemented in all three layers of the digital, analog, and antenna domains                                                                                        |

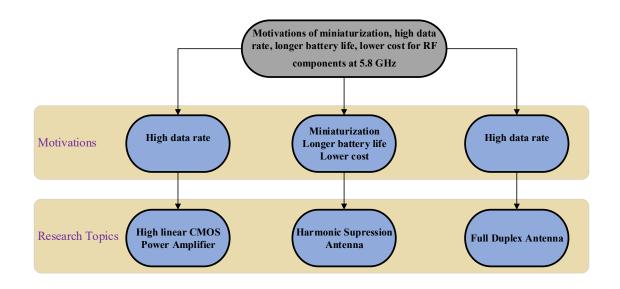

| Figure 1-5. Motivations in this thesis for RF components at 5.8 GHz ISM.                                                                                                                                                                                                    |

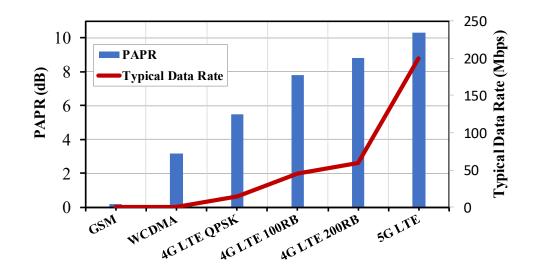

| Figure 1-6. Typical data rate and peak-to-average power ratio (PAPR) for different standards of mobile communication generations [4] [32]. The data shows that the PAPR follows the same trend as the typical data rate                                                     |

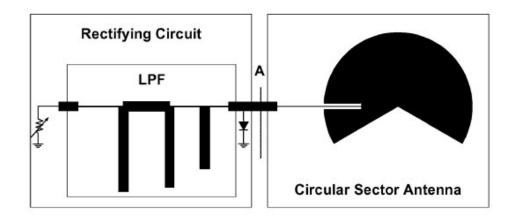

| Figure 1-7. A rectifying circuit with a harmonic suppression antenna using a circular sector antenna [33]. The circular sector shape of the antenna alters the higher order resonances, shifting them away from the harmonic frequencies                                    |

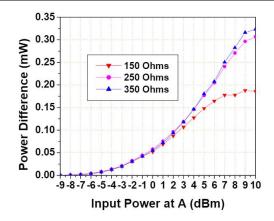

| Figure 1-8. Power difference between the rectifying circuit with the circular sector antenna (harmonic suppression antenna) at 250 and 250 Ohms and the conventional rectangular antenna at 150 Ohms [33] 9                                                                 |

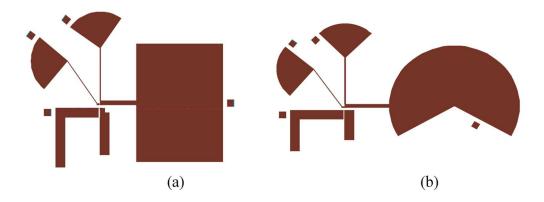

| Figure 1-9. Oscillator AIA layouts with (a) conventional rectangular patch antenna (b) and circular patch antenna                                                                                                                                                           |

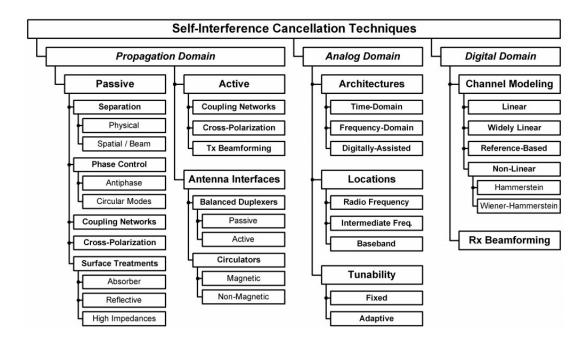

| Figure 1-10. Many self-interference cancelation techniques have been proposed in the propagation, analog and digital domains [30]                                                                                                                                           |

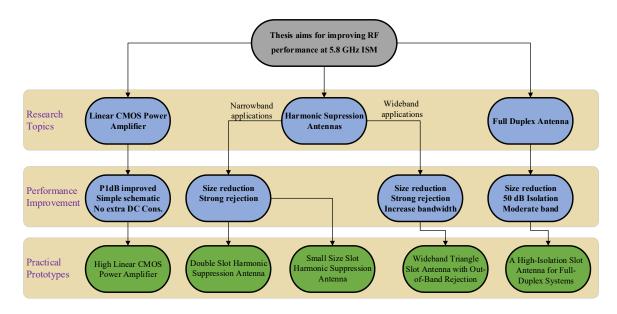

| Figure 1-11. Thesis aims for improving RF transceiver performance at 5.8 GHz ISM                                                                                                                                                                                            |

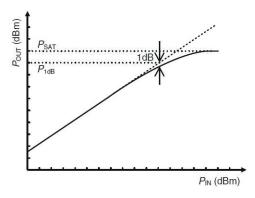

| Figure 2-1. Definition of P <sub>1dB</sub> [4]. The P <sub>1dB</sub> is the output power value at which the power gain drops one dB from its constant value                                                                                                                 |

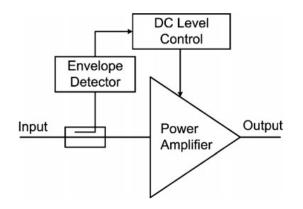

| Figure 2-2. A typical adaptive bias block diagram [13]. The envelope detector senses the strength of the input signal and the DC level control converts the signal level into a proper DC bias of the power amplifier. 26                                                   |

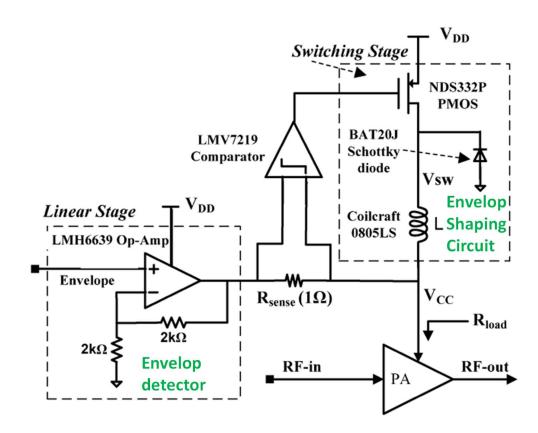

| Figure 2-3. Circuit diagram for the adaptive gate bias circuit [51]. The circuit is complicated with several operational amplifiers, attenuator, and Schottky diodes. The quality of the graph is low due to the source file                                                |

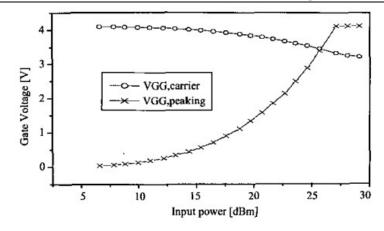

| Figure 2-4. Control shapes of the two gate voltages for the adaptively controlled power amplifier [52]. The graph shows that the gate voltage of the peaking amplifier increases adaptively with the input power. The quality of the graph is low due to the source file    |

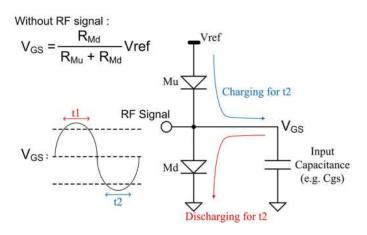

| Figure 2-5. The proposed adaptive bias scheme [13]. When the RF input signal grows large enough to turn on and off the diode Mu and Md, the proposed adaptive bias circuit begins its operation in a similar manner to a charge pump in a phase-locked loop (PLL)           |

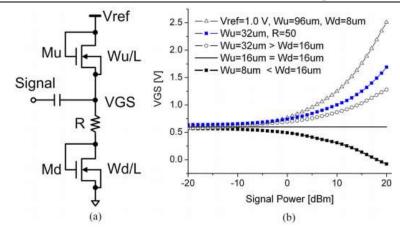

| Figure 2-6. (a) The circuit design based on the scheme in Figure 2-5. (b) The simulation results of VGS with different sizes of the Mu and Md diodes. The graph shows the bias voltage VGS follows adaptively with the signal power, i.e. input power                       |

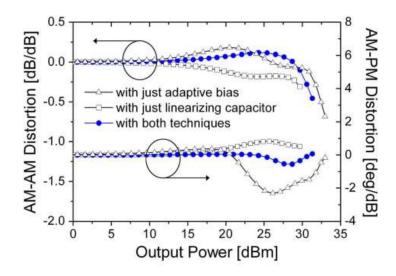

| Figure 2-7. Calculated AM-AM and AM-PM distortions. The adaptive bias technique is combined with the linearizing capacitor technique to improve both AM-AM and AM-PM distortions. The adaptive bias technique alone can provide remarkable improvement in AM-AM distortions |

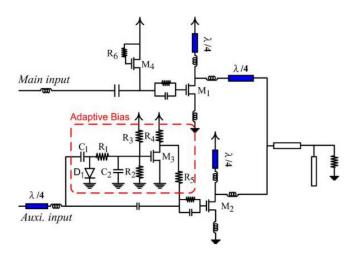

| Figure 2-8. A 2.4 GHz Doherty power amplifier (PA) with adaptive bias control circuit [14]. The adaptive bias circuit detects the RF signal extracted from the auxiliary input power                                                                                                                                                                                                                                                                                                                                                                                                                                               |

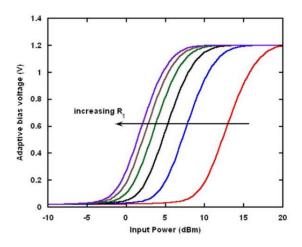

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-9. Curve of adaptive bias voltage in respect to input power. The bias voltage increases adaptively with input power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

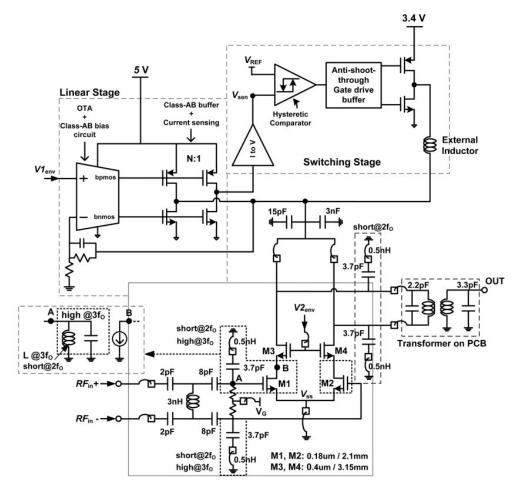

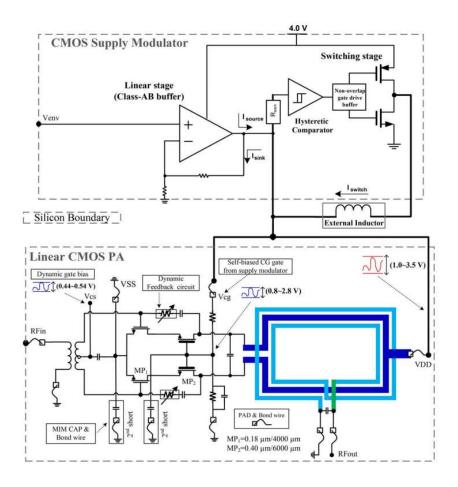

| Figure 2-10. Schematic of the envelope tracking CMOS PA with the supply modulator [5]. The second harmonic short circuits are placed at the input and output of the PA                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 2-11. (a)-(d) Simulated voltage and current waveforms of the cascode transistor and their harmonics components of the waveforms. (e) Load line in the common source (CS) transistor. (f) Load line in the common gate (CG) transistor. The input harmonic short circuit reduces the distortion generated by the nonlinear input capacitances. It also increase output power at fundamental frequency in (c), thus P <sub>1dB</sub> [5]. 31                                                                                                                                                                                  |

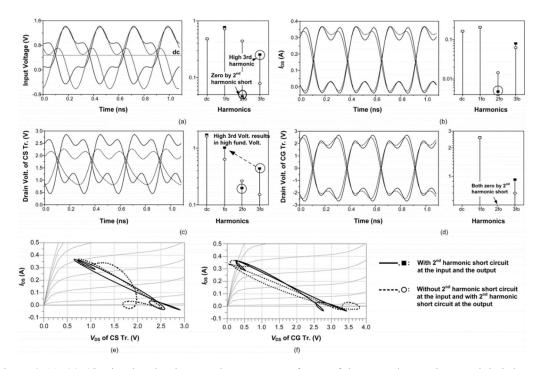

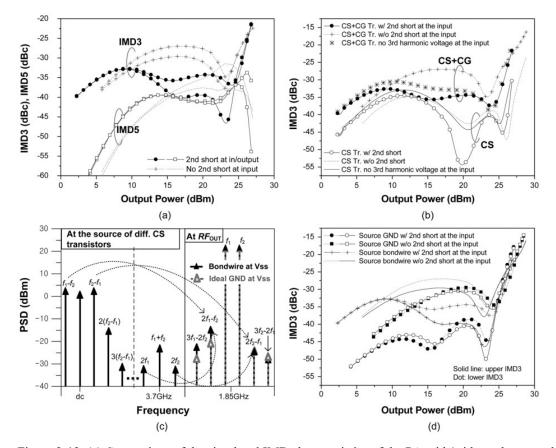

| Figure 2-12. (a) Comparison of the simulated IMD characteristics of the PA with/without the second harmonic control circuits at the input. Both PAs have the second harmonic control circuits at the output. (b) Contributions of the CS and CG transistors to the distortion in the cascode structure. The impact of the third harmonic on IMD3 is also shown in the plot. (c) Simulated intermodulation power spectral density (PSD) at the output power of 23 dBm for the case with the second harmonic short at the input. (d) Reduced IMD3 imbalance by an ideal ground at the source terminal of differential CS transistors |

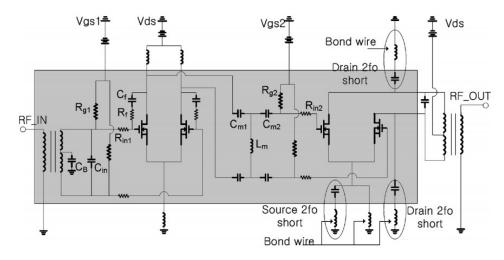

| Figure 2-13. Schematic of harmonic tuned fully differential CMOS PA [53]. The harmonic termination technique at the common source node is adopted along with normal harmonic termination at the drain 33                                                                                                                                                                                                                                                                                                                                                                                                                           |

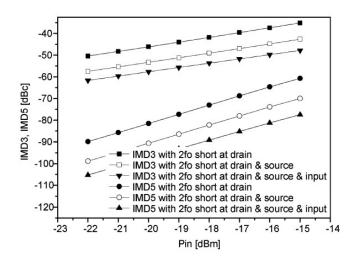

| Figure 2-14. IMD3 and IMD5 comparisons for various methods of the second harmonic terminations. The power amplifier with the second harmonic termination improves the IMD3 and IMD5 by maximally 6 dB and 7 dB, respectively                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 2-15. Second harmonic short circuit is in combination with the adaptive bias techniques [7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 2-16. Top view of the proposed DGS patch antenna. A H-shaped DGS is etched at the inset cut of the patch antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

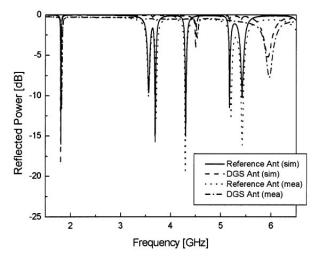

| Figure 2-17. Simulated and measured return losses. The DGS antenna provides low return loss at higher order harmonic frequencies at the expense of a small reduction in operating bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                        |

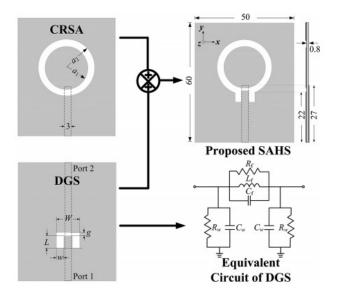

| Figure 2-18. Design evolution of proposed slot antenna with harmonic suppression [57]. An inverted U-shaped DGS is inserted into a circular ring slot antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

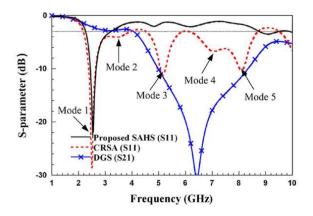

| Figure 2-19. Simulated $S_{11}$ of proposed antenna and CRSA, and $S_{21}$ of DGS [57]. The inverted U-shaped DvGS provide a stopband between 3 and 8.6 GHz in expense of small reduction in operating bandwidth 41                                                                                                                                                                                                                                                                                                                                                                                                                |

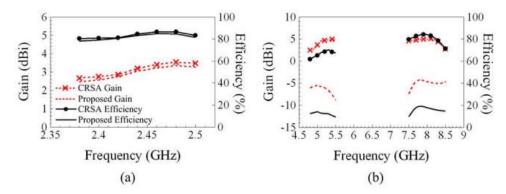

| Figure 2-20. Measured peak gain and efficiency variation of the proposed antenna and CRSA [57] across (a) the fundamental frequency and (b) the second and the third harmonic frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 2-21. Configuration of the CPW-fed inductively coupled slot antenna proposed in [60]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

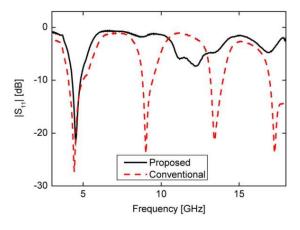

| Figure 2-22. Measured $ S_{11} $ of the proposed and conventional uniform antenna [60]. The proposed antenna shows low return loss at high-order harmonic frequencies. The data also shows that the operating bandwidth of the harmonic suppression antenna reduces compared to the conventional uniform antenna                                                                                                                                                                                                                                                                                                                   |

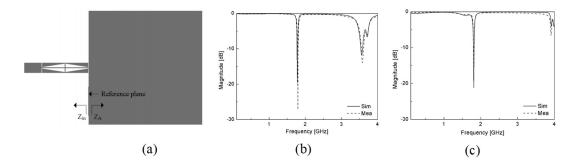

| Figure 2-23. (a) Schematic diagram of a patch antenna [64] with a compact microstrip resonant cell (CMRC).(b) S-parameters of the conventional antenna. (c) S-parameters of the harmonic suppression antenna. Comparison between that (b) and (c) show that the CMRC can provide stopband until the second harmonic frequency                                                                                                                                                                                                                                                                                                      |

| Figure 2-24. (a) (b) Schematic diagram of inset fed square patch antenna [65] fed by a DGS integrated microstrip line and an open stub (MIM cap). (b) S-parameters of the conventional antenna. (c) S-parameters of the harmonic suppression antenna. Comparison between that (b) and (c) show that the DGSs and MIM cap can provide stopband until the third harmonic frequency                                                                                                                                                                                                                                                   |

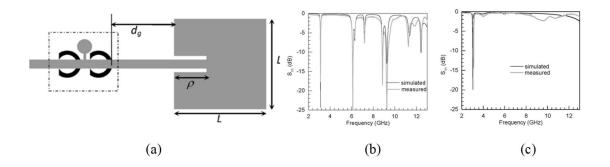

| Figure 2-25. The T-shaped fed slot harmonic suppression antenna [54]. A compact harmonic suppression structure is inserted totally inside the main radiating slot                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

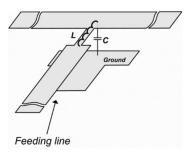

| Figure 2-26. Zoomed view of harmonic suppression structure of input feedline region [54]. The thin microstrip line and the MIM cap acts like a LC low pass filter                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-27. The simulated and measured return losses of the T-shaped slot antenna [54]. The proposed harmonic supersession antenna has small return loss at the second and third harmonic frequencies                                                                                        |

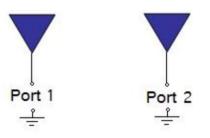

| Figure 2-28. Two-port antenna network                                                                                                                                                                                                                                                         |

| Figure 2-29. (a) Bottom and (b) top layers of the proposed antenna with a T-shaped DGS and a coupler [42]                                                                                                                                                                                     |

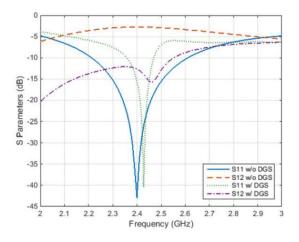

| Figure 2-30. Effect of DGS on S-parameters [42]. The DGS improves the isolation S <sub>21</sub> by 12 dB 50                                                                                                                                                                                   |

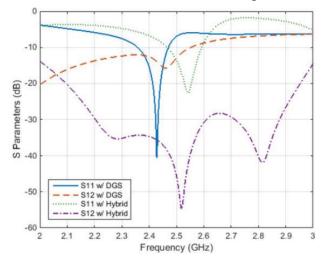

| Figure 2-31. Effect of hybrid on S-parameters [42]. The data show that the hybrid improves isolation to 35 dB                                                                                                                                                                                 |

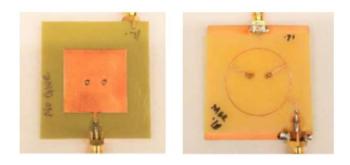

| Figure 2-32. Fabricated prototype for proposed antenna [43]. The hybrid is connected in series with the antenna to improve the isolation                                                                                                                                                      |

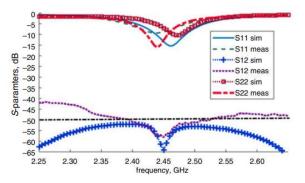

| Figure 2-33. Simulated and measured S-parameters [43]. The data shows a 50 dB isolation with limited bandwidth                                                                                                                                                                                |

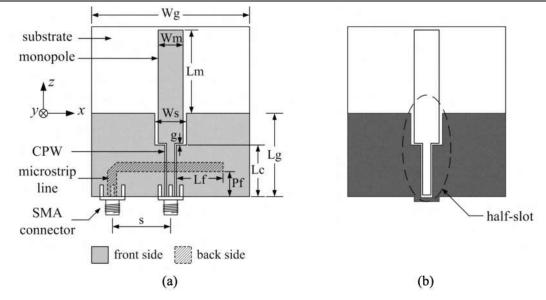

| Figure 2-34. (a) Configuration of the antenna which includes two SMA ports [68]. (b) Schematic sketch of the half-slot                                                                                                                                                                        |

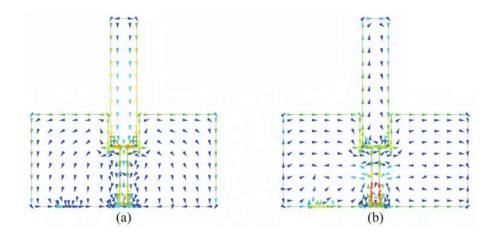

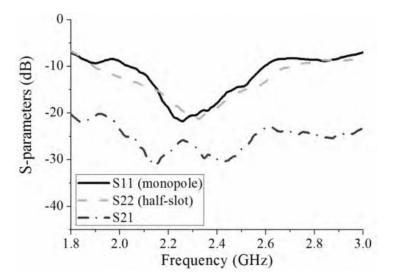

| Figure 2-35. Simulated current distribution [68]: (a) the monopole is excited; (b) the half-slot antenna is excited. 53                                                                                                                                                                       |

| Figure 2-36. Measured S-parameters show an isolation of better than 23 dB across the measured bandwidth [68]                                                                                                                                                                                  |

| Figure 2-37. Geometry of the proposed CPW antenna [41]. The antenna have two ports which can excite the even and odd modes                                                                                                                                                                    |

| Figure 2-38. Electric field distribution in CPW: (a) odd mode when port 1 is excited and (b) even mode when port 2 is excited [41]                                                                                                                                                            |

| Figure 2-39. Measured and simulated S-parameter of the proposed antenna                                                                                                                                                                                                                       |

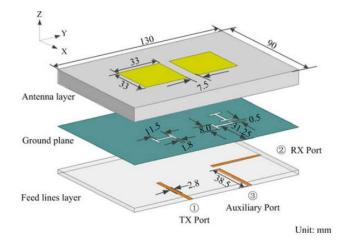

| Figure 2-40. Three-dimensional geometry of the aperture-coupled microstrip patch antenna pair with an auxiliary port [46]                                                                                                                                                                     |

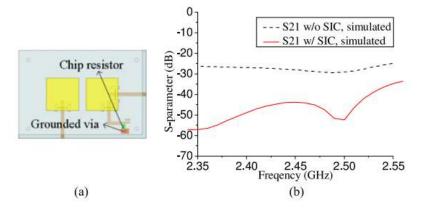

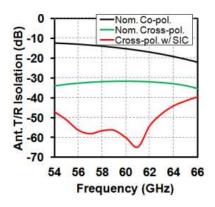

| Figure 2-41. (a) Perspective of the antenna pair with the reflective terminal. (b) Simulated S21 of the antenna pair with and without SIC [46]. The SIC improves the isolation from 25 dB to 35-57 dB across bandwidth                                                                        |

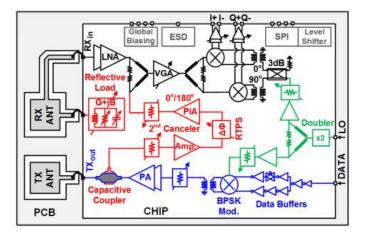

| Figure 2-42. Architecture of the full-duplex 60 GHz TX and RX with reconfigurable polarization-based antenna and RF cancellation [72]. The reflective load is to control the reflection coefficient of the auxiliary port in RX antenna to get very low coupling or isolation with TX antenna |

| Figure 2-43. The simulation isolation with the SIC using auxiliary port improves from 30 dB to around 50 dB across 8 GHz in simulation [72]                                                                                                                                                   |

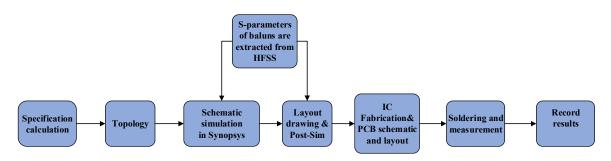

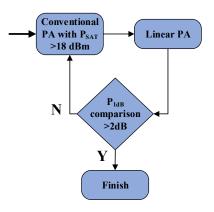

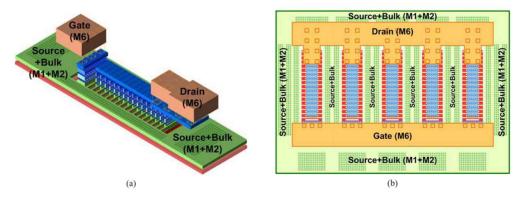

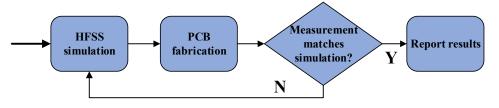

| Figure 3-1. Design process of the CMOS Power Amplifier                                                                                                                                                                                                                                        |

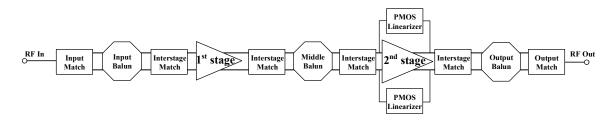

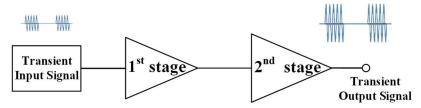

| Figure 3-2. The conventional two-stage power amplifier with matching networks                                                                                                                                                                                                                 |

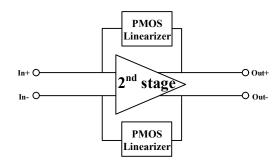

| Figure 3-3. The linear power amplifier with PMOS linearisers                                                                                                                                                                                                                                  |

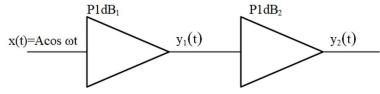

| Figure 3-4. The cascaded combination of a class A and class B amplifiers to improve linearity. <i>Acoswt</i> is the input signal fed to the amplifier 1 [11, 76]                                                                                                                              |

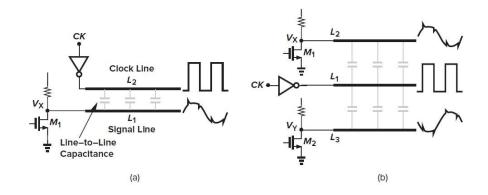

| Figure 3-5. (a) Degradation of a signal due to coupling to a clock line; (b) Coupling reduction due to differential operation [79]                                                                                                                                                            |

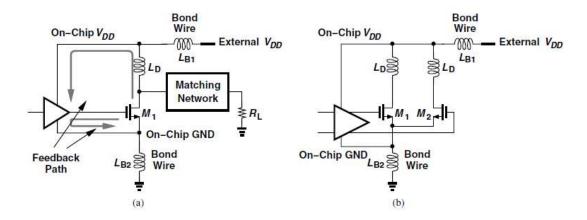

| Figure 3-6. (a) Feedback in a single-ended PA due to bond wires, (b) less problematic situation in a differential PA [75]                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

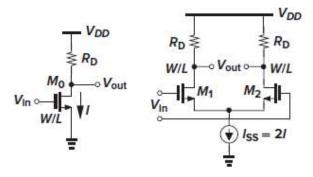

| Figure 3-7. Single-ended and differential amplifier with same voltage gain [79]                                                                                                                                                                                                                                                         |

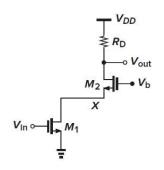

| Figure 3-8. Basic Cascode Configuration [75]                                                                                                                                                                                                                                                                                            |

| Figure 3-9. Input-output characteristics of a cascode stage [75]                                                                                                                                                                                                                                                                        |

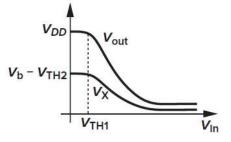

| Figure 3-10. (a) Cascode PA and(b) its waveforms [75]. Both $V_X - V_b$ and $V_Y$ are smaller than $V_{DD}$                                                                                                                                                                                                                             |

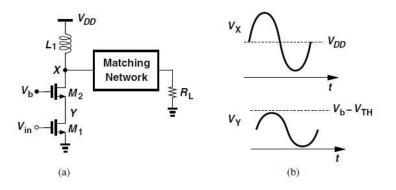

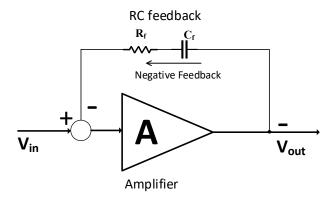

| Figure 3-11. RC feedback network, including R <sub>f</sub> and C <sub>f</sub> , using with cascode configuration                                                                                                                                                                                                                        |

| Figure 3-12. Negative feedback concept for a general amplifier [50] [75]. A is the gain of the amplifier 72                                                                                                                                                                                                                             |

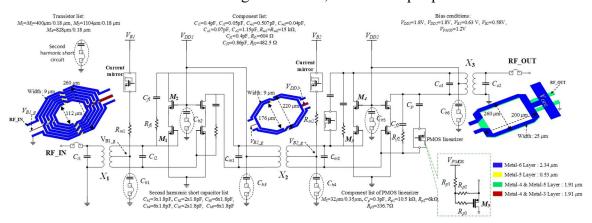

| Figure 3-13. The linear PA schematic with PMOS linearisers                                                                                                                                                                                                                                                                              |

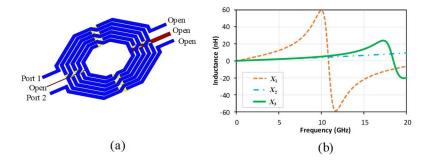

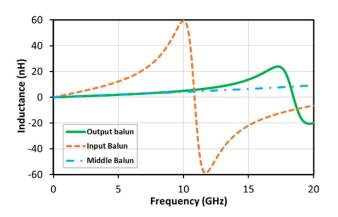

| Figure 3-14. Simulated inductance of transformers. (a) Simulation setup. (b) Self-resonance frequencies (inductance=0) >> 5.8 GHz                                                                                                                                                                                                       |

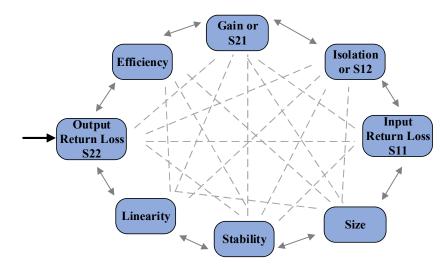

| Figure 3-15. Optimization process of the conventional and linearity PA schematics and layouts in Synopsys. The schematic optimization process does not have the parameter "Size"                                                                                                                                                        |

| Figure 3-16. Design process of the linear PA schematic                                                                                                                                                                                                                                                                                  |

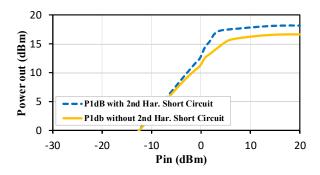

| Figure 3-17. Comparison between $P_{1dB}$ curves, with and without $2^{nd}$ short harmonic circuit                                                                                                                                                                                                                                      |

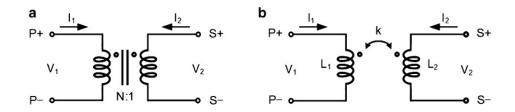

| Figure 3-18. Schematic symbol of (a) an ideal N : 1 transformer and (b) a transformer made of two coupled inductors [82]                                                                                                                                                                                                                |

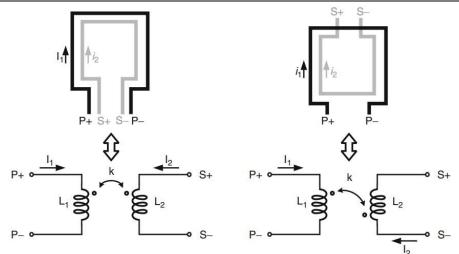

| Figure 3-19. Transformer with different coupling directions and the schematic symbols [82] [80]                                                                                                                                                                                                                                         |

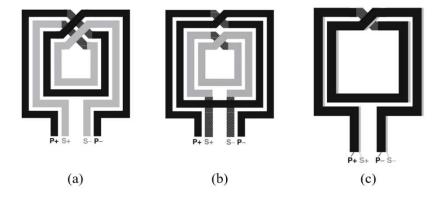

| Figure 3-20. Three layout types of on-chip transformers. (a) Interleaved type, (b) Taped type, and (c) stacked layout                                                                                                                                                                                                                   |

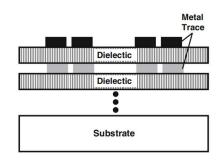

| Figure 3-21. Cross-section view of a CMOS process [82] [80]                                                                                                                                                                                                                                                                             |

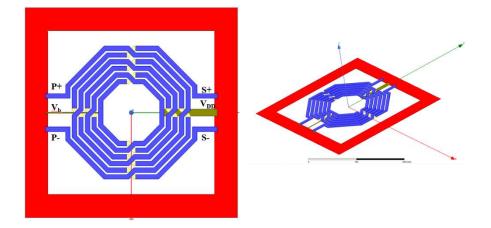

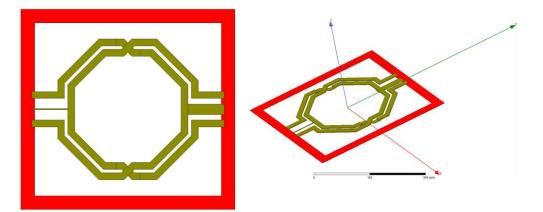

| Figure 3-22. HFSS simulation setup of input TLT from a front view and 3D view                                                                                                                                                                                                                                                           |

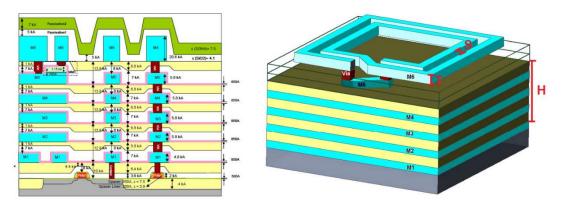

| Figure 3-23. Scheme of cross-section of interconnection structure in a typical 180 um TSMC and its 3D structure [83]                                                                                                                                                                                                                    |

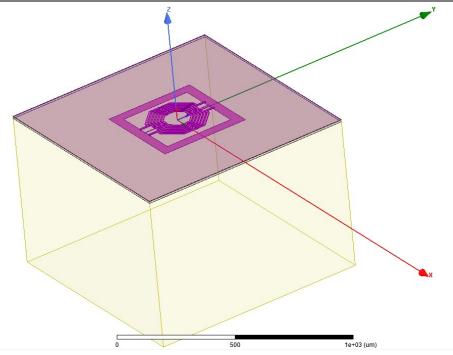

| Figure 3-24. 3D HFSS setup model of the balun simulation in the TSMC substrate                                                                                                                                                                                                                                                          |

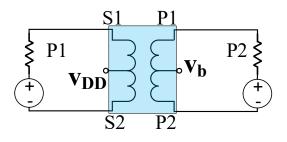

| Figure 3-25. Synopsys test bed setup for extracting the L, R, Q value and coupling factor K. The test bed is used to check the self-resonant frequency as well                                                                                                                                                                          |

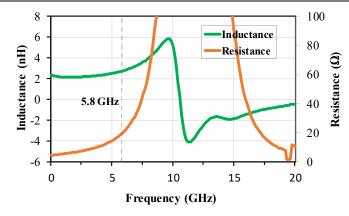

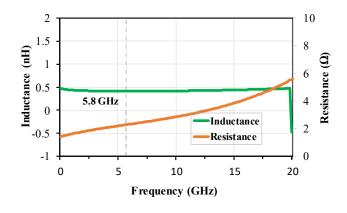

| Figure 3-26. Simulated results of inductance value L (nH) and resistance value $R(\Omega)$ . The self-resonace frequency is near 10 GHz where the inducance is equal to zero                                                                                                                                                            |

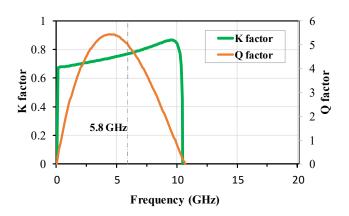

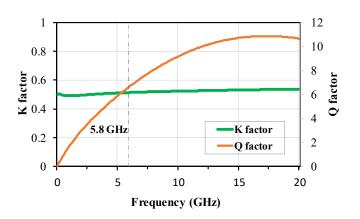

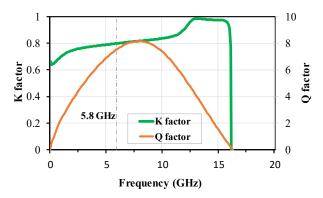

| Figure 3-27. Simulated results of inductance K factor and Q factor                                                                                                                                                                                                                                                                      |

| Figure 3-28. HFSS simulation model of the middle TLT                                                                                                                                                                                                                                                                                    |

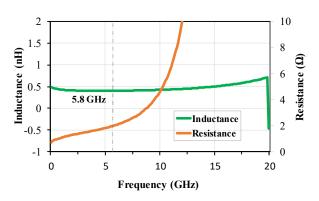

| Figure 3-29. Simulated results of inductance value L (nH) and resistance value $R(\Omega)$                                                                                                                                                                                                                                              |

| Figure 3-30. Simulated results of coupling K factor and Q factor                                                                                                                                                                                                                                                                        |

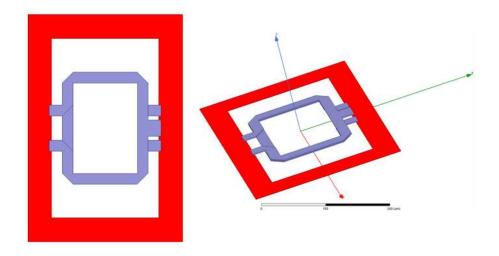

| Figure 3-31. HFSS simulation model of the output TLT. The output TLT is chosen in stack type because of the higher coupling factor, thus lower loss. The rectangular shape is to keep the horizontal size of the TLT small and constant while the vertical side can be adjusted. This helps to save layout space in the horizontal size |

| Figure 3-32. Simulated results of inductance value L (nH) and resistance value R(Ω)                                                                                                                                                                                                                                                     |

| Figure 3-33. Simulated results of coupling K factor and Q factor                                                                                                                                                                                                                                                                        |

| Figure 3-34. Simulated inductance of transformers. Self-resonance frequencies (cross-zero inductance line) are much higher than operating frequency 5.8 GHz                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-35. Block diagram of the 2 <sup>nd</sup> stage or the power-stage with the PMOS lineariser                                                                                                                                                                                                                                                                 |

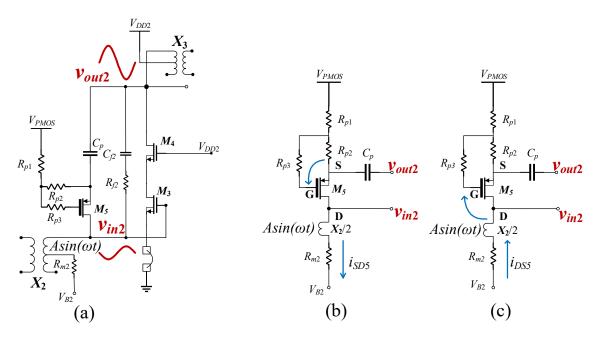

| Figure 3-36. a) PMOS linearizer. (a) Schematic of the PMOS linearizer in the PA. (b) When $M_5$ conducts from S to D. (c) When $M_5$ conducts from D to S. <i>Asin wt</i> is the output of the 1 <sup>st</sup> stage                                                                                                                                                |

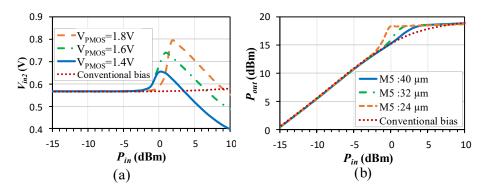

| Figure 3-37. Simulated two parameters versus $P_{in}$ . (a) $V_{in2}$ with different $V_{PMOS}$ . (b) $P_{out}$ with different widths of $M_5$                                                                                                                                                                                                                      |

| Figure 3-38. A sample of the simulated k factor versus the frequency of the whole PA in the schematic simulation. The k factor can also be calculated directly from the simulated S-parameters. The k factor must be larger than 1 in all frequencies                                                                                                               |

| Figure 3-39. Test circuit in simulation for stability, on-off input signal                                                                                                                                                                                                                                                                                          |

| Figure 3-40. Test circuit in simulation for stability, on-off supply voltages                                                                                                                                                                                                                                                                                       |

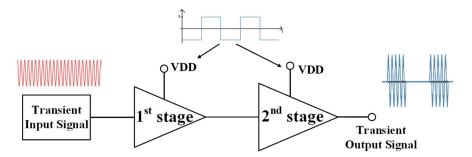

| Figure 3-41. The 3D layout in [86]. (a) 3D layout of a single unit. (b) 2D layout of 5 units. The gate and drain of transistors are connected from metal layer 1 to metal layer 6 to reduce parasitic resistance                                                                                                                                                    |

| Figure 3-42. Schematic of the 1 <sup>st</sup> stage. The M1 transistor is divided into 8 parallel transistors                                                                                                                                                                                                                                                       |

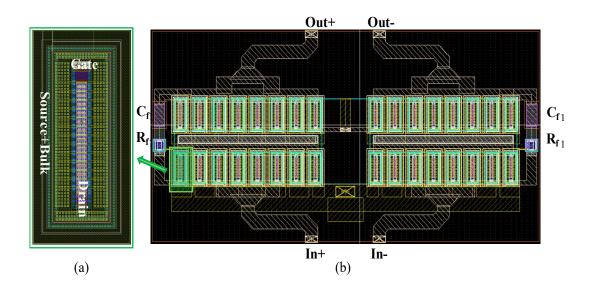

| Figure 3-43. (a) Layout of a transistor containing 25 fingers of 2 $\mu$ m width for each finger. (b) Layout of the 1 <sup>st</sup> stage. The feedback capacitor and resistor are C <sub>f1</sub> =0.4pF and R <sub>f1</sub> =604 $\Omega$ , respectively                                                                                                          |

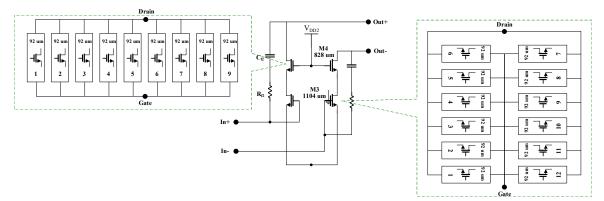

| Figure 3-44. Schematic of the 2 <sup>nd</sup> stage. The layouts of M3 are folded to save space                                                                                                                                                                                                                                                                     |

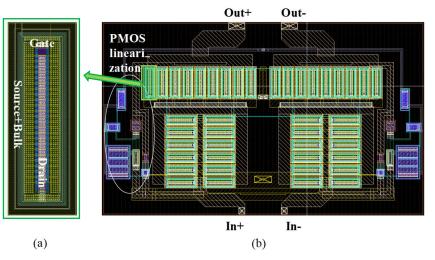

| Figure 3-45. (a) Layout of a transistor containing 46 fingers of 2 µm width for each finger. (b) Layout of the 2 <sup>nd</sup> stage with PMOS linearization                                                                                                                                                                                                        |

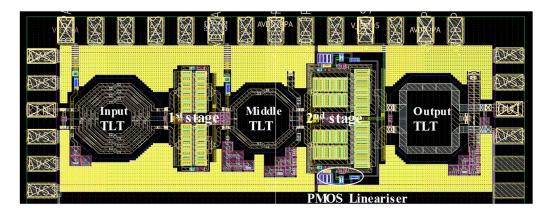

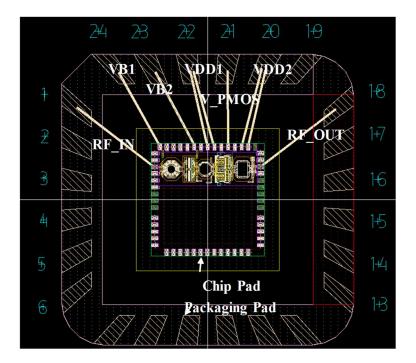

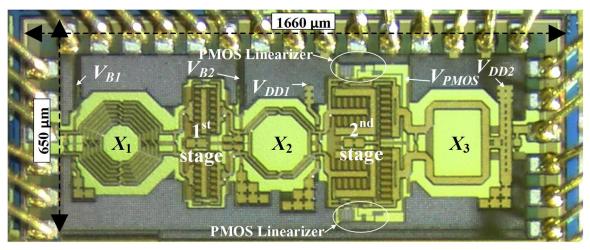

| Figure 3-46. Die micro-photo of the proposed PA. The chip size is 1.441 x 0.543 mm2 including the fillers in the yellow colour                                                                                                                                                                                                                                      |

| Figure 3-47. Bondwire in a chip [87]                                                                                                                                                                                                                                                                                                                                |

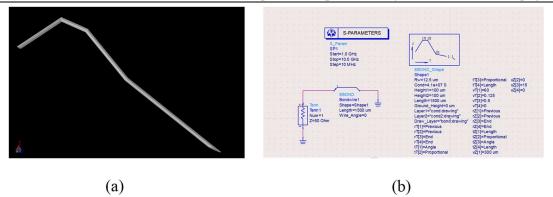

| Figure 3-48. (a) 3D model of a bondwire in ADS, (b) ADS simulation setup                                                                                                                                                                                                                                                                                            |

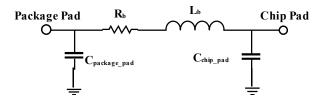

| Figure 3-49. Equivalent circuit model of a bondwire. The values used in this design are: $R_b=0.056 \Omega$ , $L_b=1.37 \text{ nH}$ , $C_{package_pad}=0.416 \text{ pF}$ , and $C_{chip_pad}=0.12 \text{ pF}$                                                                                                                                                       |

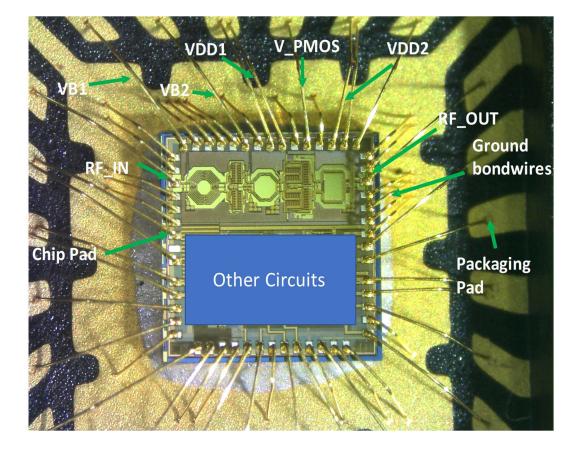

| Figure 3-50. The normal bondwire diagram of the proposed PA. The normal bondwires connect the bond pad in the chip, or chip pad, to the pin lead in the package, or the packaging pad                                                                                                                                                                               |

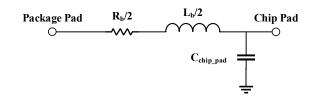

| Figure 3-51. Equivalent circuit model of a ground bondwire                                                                                                                                                                                                                                                                                                          |

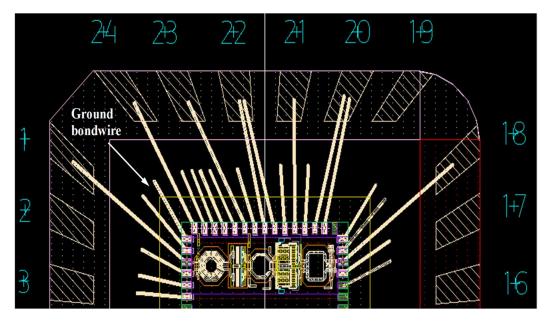

| Figure 3-52. The ground bondwire diagram of the proposed PA. The ground bondwires (shorter ones) are connected from the chip pad to the ground ring of the chip, not to the package pad                                                                                                                                                                             |

| Figure 3-53. The fabrication photograph of the proposed PA100                                                                                                                                                                                                                                                                                                       |

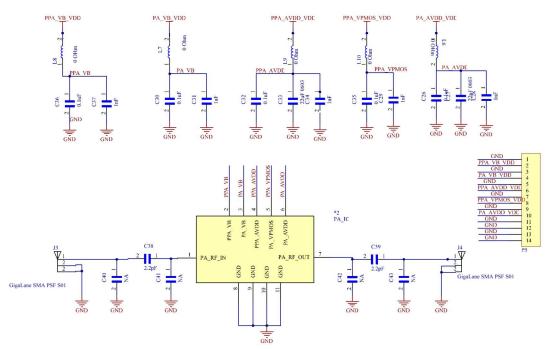

| Figure 3-54. PCB schematic for the proposed PA. The capacitors 0.1 uF, 22 uF, and 1 nF are used to filter noise from the DC power supplies. Two high RF quality GigaLane SMAs are connected to the RF input and RF output of the PA chip through coupling 2.2 pF caps. Here, PPA coresponds to 1 <sup>st</sup> stage and PA coresponds to the 2 <sup>nd</sup> stage |

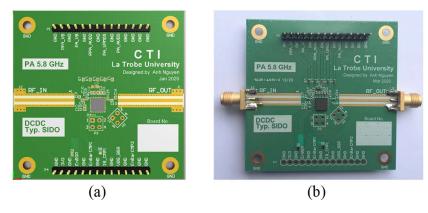

| Figure 3-55. (a) Altium 3D view of PCB layout for the proposed PA.(b) The fabricated prototype has soldered GigaLane SMA connectors and other soldered components. Here, PPA coresponds to 1 <sup>st</sup> stage and PA coresponds to the 2 <sup>nd</sup> stage                                                                                                     |

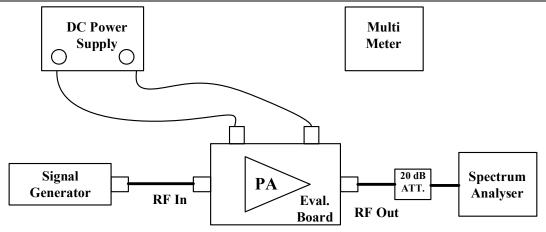

| Figure 3-56. Test setup for S-parameter measurement                                                                                                                                                                                                                                                                                                                 |

| Figure 3-57. Test setup for power_out/power_in curve measurement. The P <sub>1dB</sub> can be read from this curve. 103                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 3-58. Microphotograph of the fabricated PA. The size is 1.660 x 0.650 mm <sup>2</sup>                                                                                                                                                                                                                                                 | 103 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

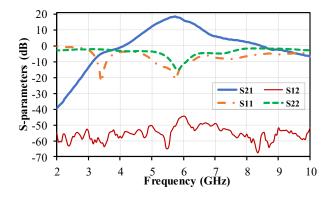

| Figure 3-59. Measured S-parameters of the whole PA                                                                                                                                                                                                                                                                                           | 103 |

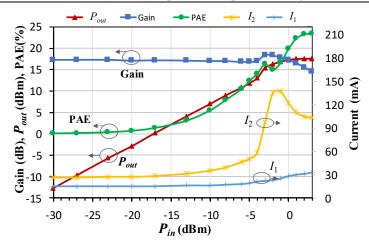

| Figure 3-60. Measured PAE, gain and power curve of the whole PA                                                                                                                                                                                                                                                                              | 104 |

| Figure 4-1. Design process for antennas based on HFSS simulation.                                                                                                                                                                                                                                                                            | 111 |

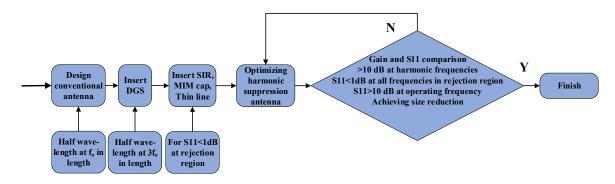

| Figure 4-2. Design process in HFSS simulation for the three harmonic suppression antennas. The process begins with designing the conventional antenna.                                                                                                                                                                                       |     |

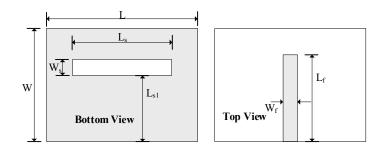

| Figure 4-3. The conventional slot antenna with a uniform rectangular shape of slot                                                                                                                                                                                                                                                           | 113 |

| Figure 4-4. Transmission line equivalent circuit of a uniform slot antenna.                                                                                                                                                                                                                                                                  | 113 |

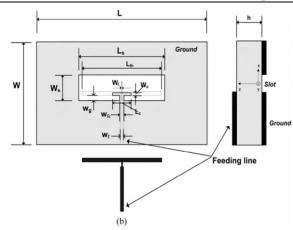

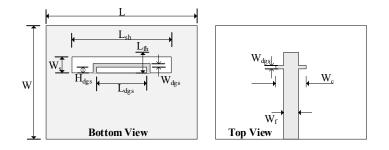

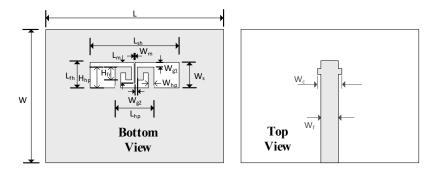

| Figure 4-5. The proposed harmonic suppression rectangular slot antenna                                                                                                                                                                                                                                                                       | 115 |

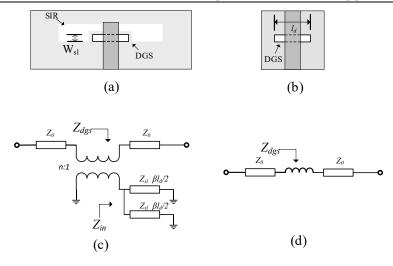

| Figure 4-6. Geometry of the DGS inside the rectangular slot antenna and its equivalent circuit. (a) DGS inside the slot antenna, (b) standalone DGS coupled with microstrip line, (c) equivalent circuit of DGS coupled with the microstrip line, (d) DGS can be equivalent to an inductor below its self-resonant freque of 3f <sub>0</sub> |     |

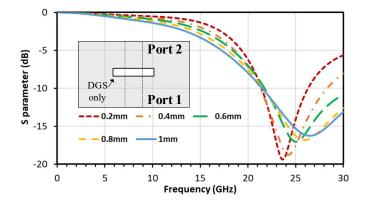

| Figure 4-7. Insertion loss of DGS only when changing its width, $W_{sl}$ . Its length equals $L_{dgs}$ which is 5.4 mm.                                                                                                                                                                                                                      | 117 |

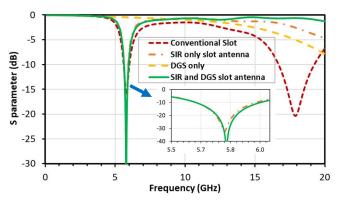

| Figure 4-8. Impact of DGS to return loss of the SIR slot antenna                                                                                                                                                                                                                                                                             | 118 |

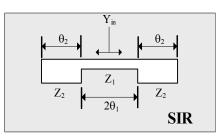

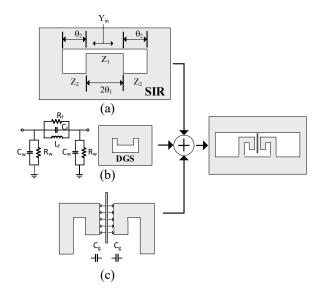

| Figure 4-9. Geometry of the SIR.                                                                                                                                                                                                                                                                                                             | 118 |

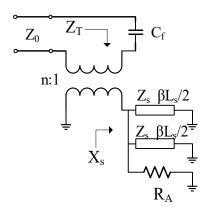

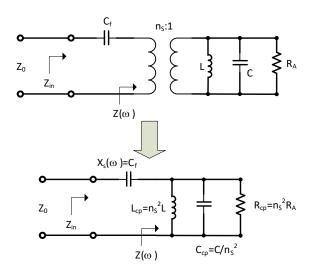

| Figure 4-10. Lumped-element equivalent circuit of the SIR antenna and its corresponding circuit withou transformer.                                                                                                                                                                                                                          |     |

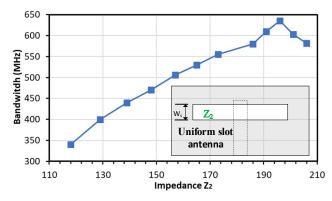

| Figure 4-11. Relationship between the bandwidth of a uniform slot antenna and the impedance of its slo<br>line ( $Z_2$ ). The resonant frequency is at 5.8 GHz.                                                                                                                                                                              |     |

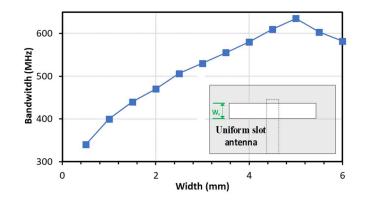

| Figure 4-12. Relationship between the bandwidth of a uniform slot antenna with the width of the slot. The resonant frequency is at 5.8 GHz.                                                                                                                                                                                                  |     |

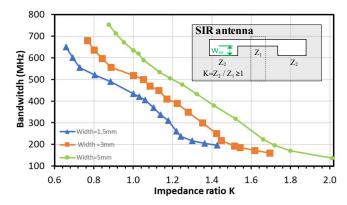

| Figure 4-13. Relationship between the bandwidth of an SIR slot antenna and the impedance ratio K (K $\geq$ The width of the slot antenna (Z <sub>2</sub> ), W <sub>s</sub> , is 1.5 mm, 3 mm and 5 mm. The resonant frequency is at 5.8 GH                                                                                                   | Iz. |

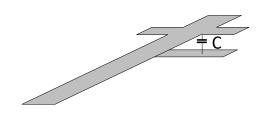

| Figure 4-14. Geometry of the MIM cap.                                                                                                                                                                                                                                                                                                        | 124 |

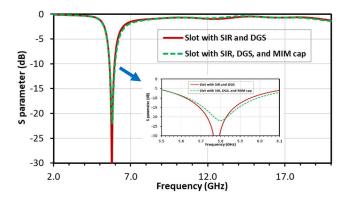

| Figure 4-15. Simulated return losses of slots with and without the MIM cap                                                                                                                                                                                                                                                                   | 125 |

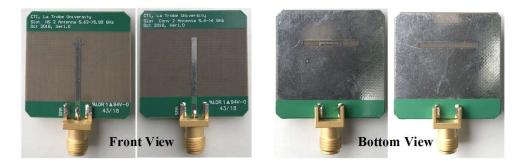

| Figure 4-16. Photograph of the fabricated antennas. The proposed antenna is on the left side of each pho<br>whereas the conventional triangle slot antenna is on the right.                                                                                                                                                                  |     |

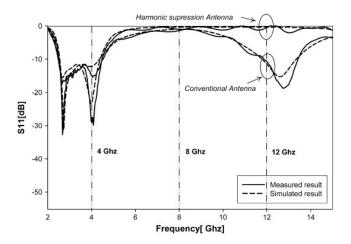

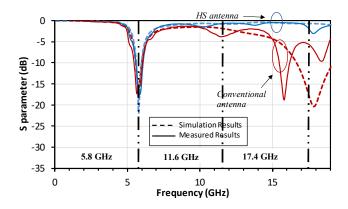

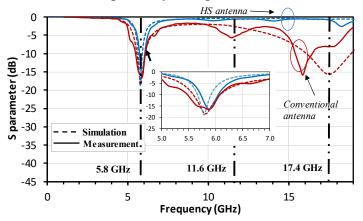

| Figure 4-17. The simulated and measured return losses of the proposed antennas. The harmonic suppres antenna has low return loss at the second and the third harmonic frequencies, compared to the conventio antenna.                                                                                                                        | nal |

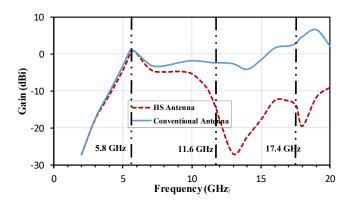

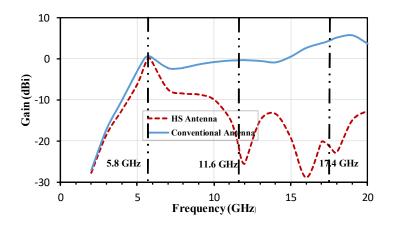

| Figure 4-18. Simulated gain in HFSS of the conventional and proposed antennas. The harmonic suppres antenna has low gain at the second and the third harmonic frequencies, compared to the conventional antenna.                                                                                                                             |     |

| Figure 4-19. Comparison of simulated radiation patterns of the proposed antennas at 5.8 GHz                                                                                                                                                                                                                                                  | 127 |

| Figure 4-20. The conventional slot antenna.                                                                                                                                                                                                                                                                                                  | 129 |

| Figure 4-21. The proposed harmonic suppression antenna.                                                                                                                                                                                                                                                                                      | 129 |

| Figure 4-22. (a) Geometry of the SIR, (b) geometry of the DGS and its equivalent circuit, (c) geometry of the fringing capacitance and meander line.                                                                                                                                                                                         | of  |

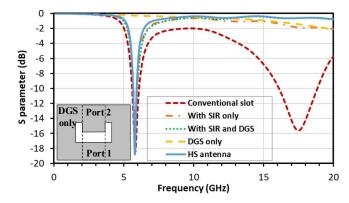

| Figure 4-23. Simulated return loss of slots with and without SIR and DGS, and simulated insertion loss of the DGS only (the geometry is in the bottom left corner)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

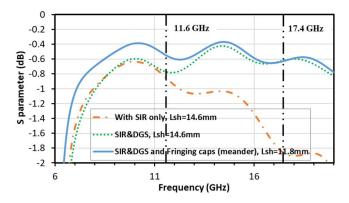

| Figure 4-24. Simulated return losses of slots from 10 GHz to 20 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 4-25. Photograph of the fabricated antennas. The proposed antenna is on the left side of each photo, whereas the conventional triangle slot antenna is on the right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 4-26. The simulated and measured return losses of the proposed antennas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 4-27. Simulated gain in HFSS of the conventional and proposed antennas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 4-28. Comparison of simulated radiation patterns of the proposed antennas at 5.8 GHz 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

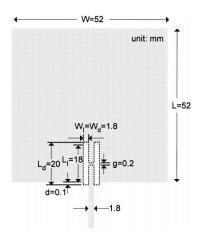

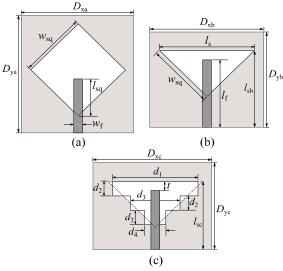

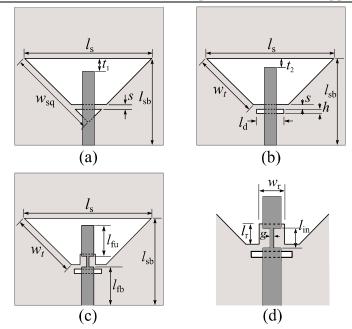

| Figure 4-29. (a) Layout of the rotated square slot antenna. (b) Right triangle slot antenna. (c) Three-section tapered slot antenna. The light grey area shows the ground metallization and the dark grey area shows the microstrip metallization. The geometrical dimensions are: $D_{xa}$ = 80 mm, $D_{ya}$ = 80 mm, $D_{xb} = D_{xc}$ = 36 mm, $D_{yb} = D_{yc}$ =32 mm, $w_{sq}$ = 24 mm, $w_{f}$ = 1.56 mm, $l_{sq}$ = 12.67 mm, $l_{sb}$ = 20.8 mm, $l_{s}$ =33.94 mm, $l_{f}$ = 16.8 mm, $l_{sb}$ = 20.8 mm, $d_1$ = 25 mm, $d_2$ = 5.7 mm, $d_3$ = 21 mm, $d_4$ = 5.4 mm, $t$ = 5.62 mm, $l_{sc}$ = 20.8 mm                                             |

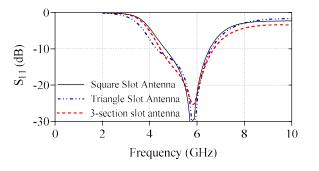

| Figure 4-30. Simulated  S11  of rotated square slot antenna, simple triangle slot antenna, and the three-<br>section slot antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 4-31. Simulated electric field at 5.8 GHz of the rotated square slot. The electric field concentrates mostly on the bottom part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

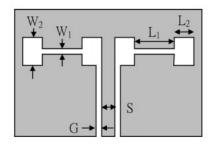

| Figure 4-32. Harmonic suppression with (a) a triangle DGS, (b) a rectangular DGS, (c) a rectangular DGS and a thin microstrip section in the feed line. (d) Zoomed view of the microstrip feed line with a narrow section coupled to a rectangular DGS. The light grey area shows the ground metallization and the dark grey area shows the microstrip metallization. The geometrical dimensions are $s = 0.6$ mm, $t_1 = 2.87$ mm, $w_t = 16.93$ mm, $h = 0.72$ mm, $l_d = 6.8$ mm, $l_{fu} = 9.1$ mm, $l_{fb} = 8.33$ mm, $l_r = 2$ mm, $w_r = 3.6$ mm, $l_{in} = 1.9$ mm, $g = 0.2$ mm. The ground plane dimensions are the same as the antenna in Fig. 1(b) |

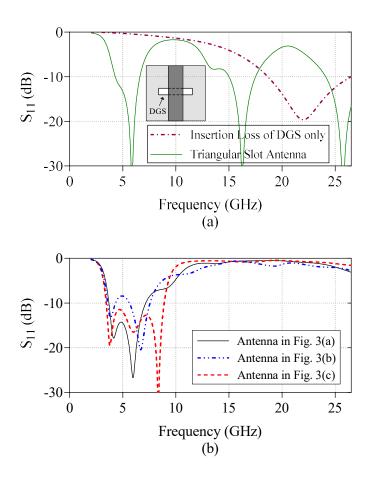

| Figure 4-33. (a) $ S_{11} $ of the reference triangle slot antenna and $ S_{21} $ of the microstrip loaded DGS shown in the inset. (b) Impact of triangle, rectangular DGSs, and thin microstrip line on the $ S_{11} $ of the triangle slot antenna.                                                                                                                                                                                                                                                                                                                                                                                                           |

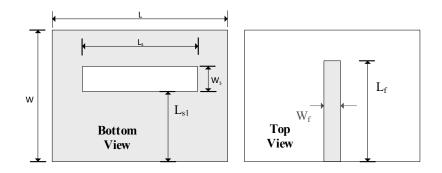

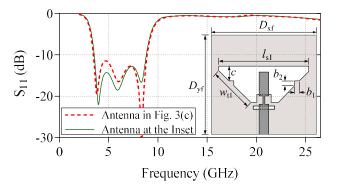

| Figure 4-34. A comparison between the simulated $ S_{11} $ antenna in Figure 4-32(c), and the final optimized antenna shown in the inset. The dimensions are $s = 0.6$ mm, $l_{s1} = 28$ mm, $c = 6.47$ mm, $w_{t1} = 9$ mm, $b_1 = b_2$ = 2.06 mm, $D_{xf} = 32$ mm, $D_{yf} = 32$ mm. All the other dimensions are the same as in Figure 4-32 (c)                                                                                                                                                                                                                                                                                                             |

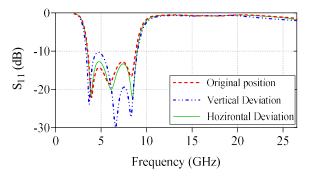

| Figure 4-35. Dimensional tolerance impact with 0.4 mm offset of the top and bottom layer in the final optimized antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 4-36. Photograph of the fabricated antennas. The proposed antenna is on the left side of each photo, whereas the simple triangle slot antenna is on the right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

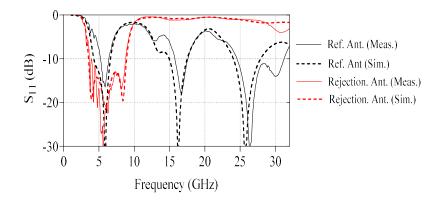

| Figure 4-37. The simulated and measured reflection coefficient of the reference and the proposed antennas.<br>142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

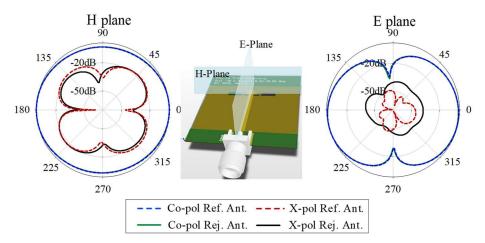

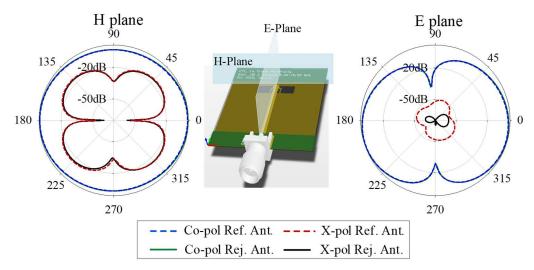

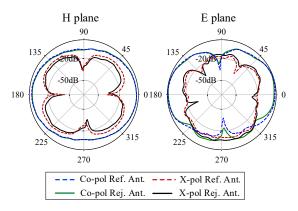

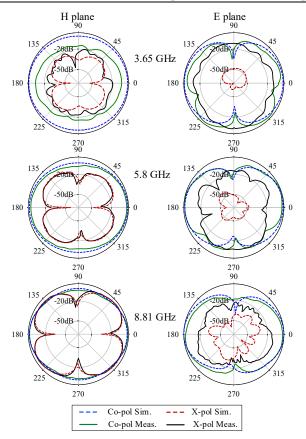

| Figure 4-38. The measured radiation pattern of the reference and the proposed antennas at 5.8 GHz 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 4-39. Simulated and measured radiation patterns of the rejection antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

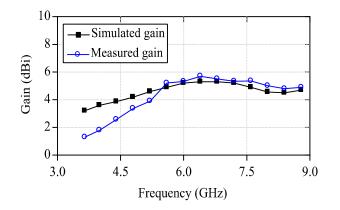

| Figure 4-40. Measured and simulated gains of the proposed antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

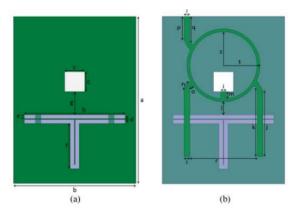

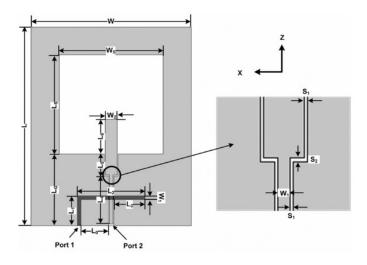

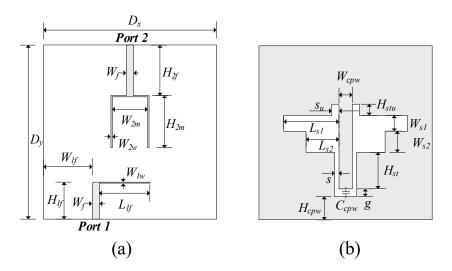

| Figure 5-1. (a) Top layer. (b) Bottom layer. The geometrical dimensions are: $D_x = 45 \text{ mm}, D_y = 40 \text{ mm}, W_f = 1.56 \text{ mm}, H_{2f} = 11.2 \text{ mm}, H_{2m} = 11.6 \text{ mm}, W_{2m} = 8 \text{ mm}, W_{2w} = 0.3 \text{ mm}, W_{1w} = 0.2 \text{ mm}, W_{1f} = 15.04, L_{1f} = 11.4 \text{ mm}, H_{1f} = 8.2 \text{ mm}, W_{cpw} = 1.4 \text{ mm}, s_u = 0.58 \text{ mm}, H_{stu} = 2.5 \text{ mm}, W_{s1} = 3.5 \text{ mm}, L_{s1} = 13.25 \text{ mm}, W_{s2} = 4.7 \text{ mm}, L_{s2} = 8.2 \text{ mm}, H_{st} = 9 \text{ mm}, s = 0.2 \text{ mm}, g = 0.8 \text{ mm}, H_{cpw} = 6.5 \text{ mm}, C_{cpw} = 0.65 \text{ pF}.$ 149        |

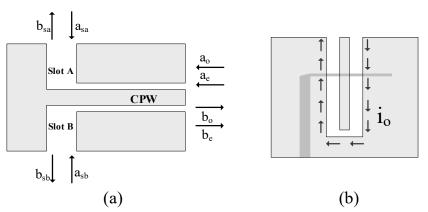

| Figure 5-2. (a) CPW-slotline tee. (b) Microstrip coupled CPW with the surface current $I_o$ in odd mode 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

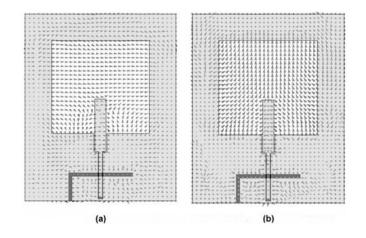

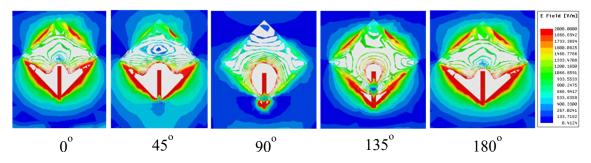

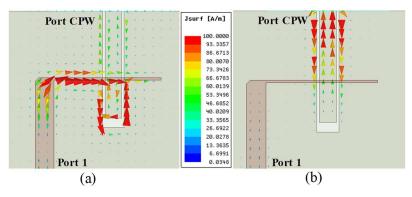

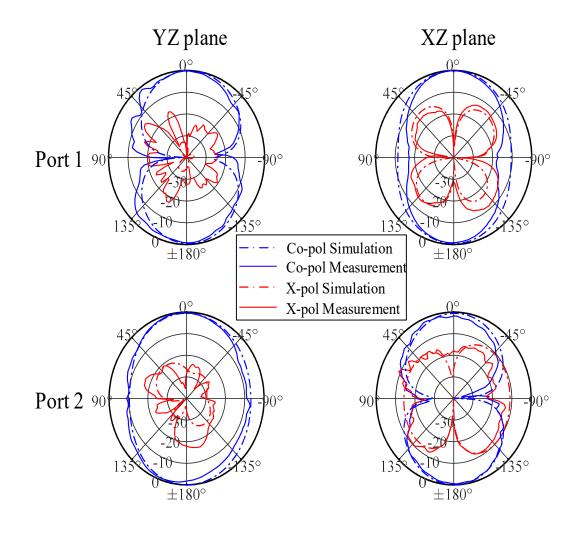

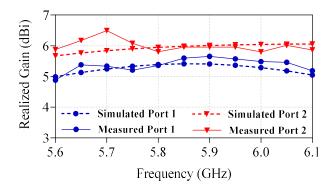

Figure 5-3. Surface current vector in CPW coupled microstrip. (a) HFSS simulation at 5.8 GHz of surface current vector in odd mode. (b) HFSS simulation at 5.8 GHz of surface current vector in even mode. ..... 150

| Figure 5-4. HFSS simulation at 5 GHz of (a) zoomed view of the surface current vector and, (b) electric field magnitude when Port 1 is excited                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

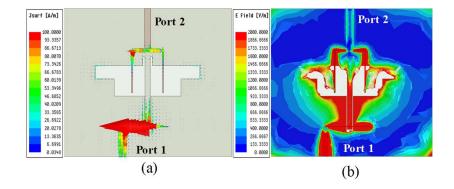

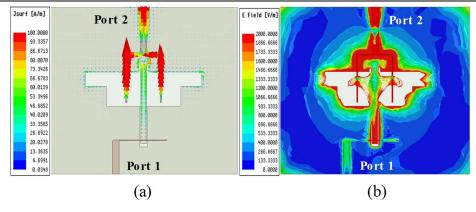

| Figure 5-5. HFSS simulation of (a) surface current vector and, (b) electric field magnitude when Port 2 is excited                                                                                                                              |

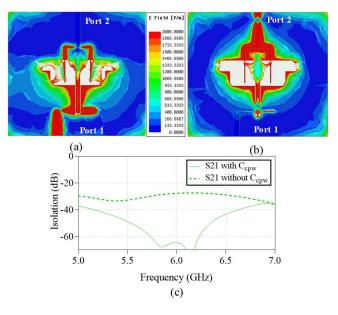

| Figure 5-6. HFSS simulation of electric field magnitude with $C_{cpw}$ when (a) Port 1 is excited, (b) Port 2 is excited, (c) Isolation in dB between the two ports                                                                             |

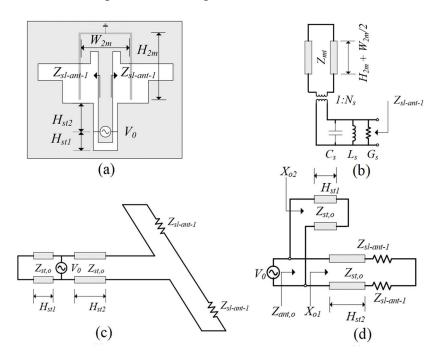

| Figure 5-7. (a) Slot antenna excited from the CPW in odd mode. (b) Impedance of the slot antenna loaded microstrip line. (c) Equivalent circuit of the proposed antenna when excited from Port 1. (d) Reduced circuit model of the slot antenna |

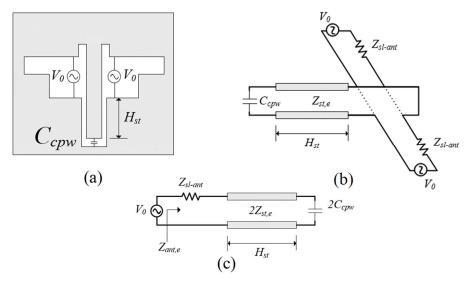

| Figure 5-8. (a) Slot antenna excited from the two thin microstrip lines in even mode in the presence of the CPW. (b) Equivalent circuit model in even mode. (c) Reduced circuit model of one slot branch                                        |

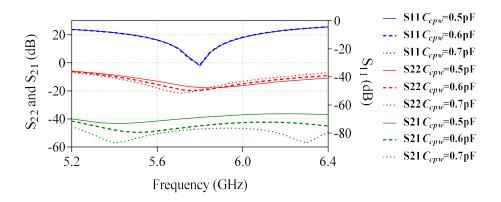

| Figure 5-9. Simulated S-parameters with different values of $C_{cpw}$                                                                                                                                                                           |

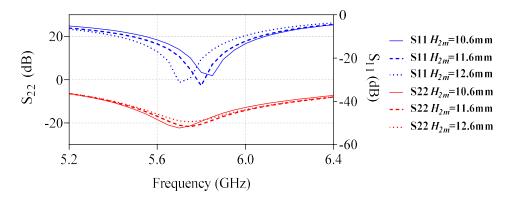

| Figure 5-10. Simulated S-parameters with different values of the quarter-wave impedance transformer $H_{2m}$ .<br>157                                                                                                                           |

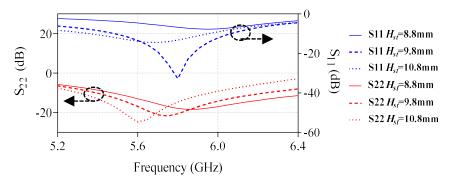

| Figure 5-11. Simulated S-parameters with different values of <i>H</i> <sub>st</sub>                                                                                                                                                             |

| Figure 5-12. Simulated S-parameters with different values of L <sub>s1</sub>                                                                                                                                                                    |

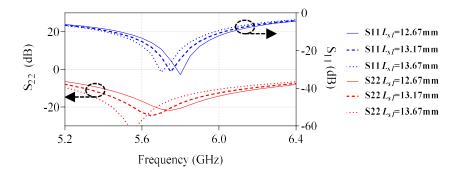

| Figure 5-13. Simplified flowchart of design guideline                                                                                                                                                                                           |

| Figure 5-14. Photographs of the fabricated antenna159                                                                                                                                                                                           |

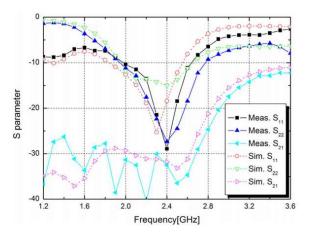

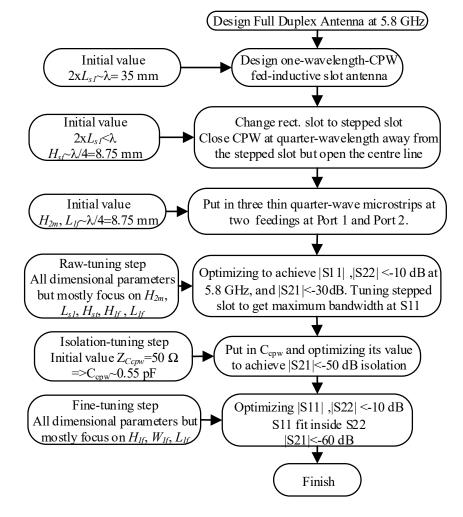

| Figure 5-15. Simulated and measured S-parameters of the proposed antenna                                                                                                                                                                        |